硅基电容器通常是单 MIM(金属-绝缘体-金属)或多 MIM 结构的静电电容器,由半导体技术制造。

硅电介质是二氧化硅 (MIS) 或氮化硅 (MOS) 绝缘层,但是能使用诸如原子层沉积 (ALD) 等半导体制造技术在硅衬底上形成其他电介质材料。高密度硅基电容器使用 3D 纳米结构电极来实现更高的表面积,从而获得更高的电容值。

二氧化硅和氮化硅等硅基电介质常用于高密度电容器。具有硅电介质的电容器非常适合需要高稳定性、可靠性和耐高温的应用。这些电容器的性能特点使其成为在恶劣环境应用中使用的合适选择。以下是硅基电介质的主要优势和局限性。

大多数电容器的性能会受到高温的显着影响。硅电容器有不同的额定温度,通常高达 250 o C。高温硅电容器适用于广泛的恶劣环境应用,包括飞机发动机控制、航空电子系统、汽车系统、井下石油勘探系统、军事应用和很快。此外,硅电容器提供高度稳定的电容性能作为电压和温度的函数。硅电容的最大容量虽然有限,但不会发生电容老化。此外,与 X7R 和 X8R 电容器不同,硅电容器的可靠性和电容在直流偏置条件下不会降低。

硅基电介质通常用于制造高密度电子器件。高密度硅电容器通常在超深沟槽中制造,它们具有非常低的漏电流和低损耗因数。无源集成连接基板 (PICS) 是实现高密度电容器的最常用技术。该工艺允许实现多芯片模块 (MCM) 和板上芯片 (COB),并有助于实现具有低功耗的更小组件。此外,这个过程允许将许多基本功能集成到一个产品中,从而有助于降造成本。通过采用最新技术,实现了高容积效率。预计随着对高性能和小型化组件的需求不断增长,硅电容器的体积效率将继续提高。到目前为止,已经实现了层比多层陶瓷电容器 (MLCC) 技术更薄的硅电容器。

漏电流是电容器经受高温时会受到影响的电容器参数之一。介电材料是决定电容器漏电流的关键因素。对介电材料施加过大应力会显着增加泄漏电流。充电电压和电介质的厚度对电容器的漏电流也有轻微的影响。与市场上大多数高温电容器相比,硅电容器具有令人印象深刻的漏电流-温度特性。此外,硅基电介质提供令人印象深刻的绝缘电阻,使其成为耦合、阻塞和定时电路的无与伦比的选择。

电容器在电子电路中有广泛的应用。因此,它们是电子系统中最常见的无源元件之一。电容器的可靠性是其故障率的一个因素。与其他无源元件相比,电容器的故障率更高。决定电容器故障率的一些关键因素包括运行时间和负载条件。比较可靠性测试表明,与高温 X8R 电容器相比,高温硅电容器具有更好的 FIT(及时故障)率。

尽管硅电容器具有出色的特性,包括高温下的高稳定性、极低的漏电流、高绝缘电阻和高电容密度,但可以实现的最大电容是有限度的。预计最新的技术进步将有助于克服这一技术限制。除了改进制造工艺外,制造商还在探索替代电介质,以解决与硅基电介质相关的主要技术障碍。

SiO 2 通常用于制造微电子器件的电容器。这些电容器是通过氧化硅并使用氧化物作为介电材料构成的。由于电容与电介质材料的面积成正比,与电介质的厚度成反比,因此电子设备制造商一直在减小电介质材料的面积和厚度,以获得小型化和高密度的设备。SiO 2 的厚度介电膜减少,通过介电材料的电荷泄漏增加。超过一定限度,由于漏电问题,电容就很难储存电荷。尽管 DRAM 制造商正在使用深沟槽来克服泄漏问题,但电介质厚度限制是微电子器件小型化的主要障碍。除了改进实施过程外,制造商还在探索替代电介质以克服这一限制。

硅基电容器通常是单 MIM(金属-绝缘体-金属)或由半导体技术构建的多 MIM 结构电容器。硅电介质是二氧化硅 (MIS) 或氮化硅 (MOS) 绝缘层,但是能够正常的使用诸如原子层沉积 (ALD) 等半导体制造技术在硅衬底上形成其他电介质材料。高密度硅基电容器使用 3D 纳米结构电极来实现更高的表面积,从而获得更高的电容值。

半导体和 MOS 电容器的结构——其带隙图、功函数和电子亲和性概念超出了本文的范围。我们将重点介绍市场上的硅基电容器及其主要特性。

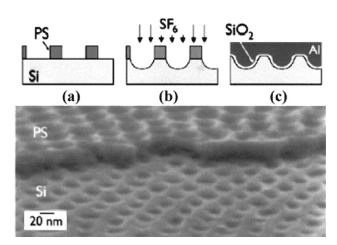

硅基电介质通过半导体制造工艺用于高密度电子器件的半导体制造工艺中。用于电容器技术的硅基电介质通常基于二氧化硅 (MIS) 或氮化硅 (MOS) 绝缘层。图 1. 下面描述了制造硅电容器的传统 MOS 技术。

在片上系统 (SiP) 或片上 (SoP) 中异质集成为多芯片模块或倒装芯片与其他技术(CMOS、MEMS 等)

硅基电介质用来制造具有极高温度稳定性、高击穿电压和低泄漏参数的低损耗、高 Q 电容器。主要限制是相对较低的介电常数。

金线或铝线热超声和超声波键合是射频应用中组装单层硅电容器 (SLC) 的最常见方式。端接样式可能会有所不同,并且可以针对环氧树脂或焊片贴装技术进行优化。

硅薄膜电容器通常基于沉积在衬底上的单层氧化硅/氮化硅电介质,并封装在类似芯片 MLCC 的设计中。它提供了非常低的电容值 (0.05pF) 和非常严格的电容容差 (±0.01pF) 的独特能力。薄膜技术保证了高频参数的最小批次变化,因此它是射频和微波滤波器的理想组件。

然而,术语“薄膜电容器”涉及更广泛的薄膜技术,该技术还使用其他电介质,例如沉积在各种衬底类型(如氧化铝、石英、硅或硅晶片)上的陶瓷或有机薄膜。

因此,“薄膜”(沉积在硅基板上)和“硅”电容器之间的区别在某种程度上是一种营销让步,尽管根据预期应用,两者之间存在显着差异。

针对射频调谐和匹配应用的器件往往是针对参数稳定性和一致性进行了优化的低电容单层器件,通常采用标准 JEDEC 封装尺寸。

相比之下,用于电源去耦、宽带 DC 阻断和类似应用的器件允许更大的容差,有利于实现更高的比电容,并且更有可能在适用于先进组装方法的封装中找到,例如引线键合或嵌入印刷电路板。然而,无论预期的应用如何,薄膜和硅电容器系列中的器件都是高性能产品,并且定价相应,目前的价格是具有类似电容和额定电压的陶瓷器件价格的 5 到 5000 倍。

高密度硅电容器通常制造在超深沟槽中以增加电极的表面积。它们有很低的漏电流和低损耗因数。无源集成连接基板 (PICS) 是实现高密度电容器的最常用技术。该工艺允许实现多芯片模块 (MCM) 和板上芯片 (COB),并有助于实现具有低功耗的更小组件。此外,这样的一个过程允许将许多基本功能集成到一个产品中,从而有助于降造成本。参见图 5。右侧 - 3D PICS 电容器结构。

通过采用最新的 3D 技术,已经实现了超过 450nF/mm2 的高容积效率。硅电容器可以在 100 微米以下的层中制造,比多层陶瓷电容器 (MLCC) 技术薄 4 倍。与 MLCC 电容器相比,制造的硅电容器声称其可靠性提高了 10 倍,结合高达 250C 的超高温稳定性,高密度硅电容器技术可在汽车、工业/石油钻探或航空航天/国防工业中实现大量高要求应用. 预计随对高性能和小型化组件的需求一直增长,硅电容器的体积效率将继续提高。

集成电容器和无源器件有很多用途。它们在 PCB 上占用的空间更少,它们简化了设计,并且由于更紧密的组件匹配,它们能通过正确的工艺缩小电路公差。缺点是,和半导体一样,体积就是一切。

尽管将无源元件保持在芯片外的一个常见原因是它们的尺寸相对于片上晶体管的尺寸——不值得在组装成本高于其材料价值的设备上浪费宝贵的硅面积——许多现成的零件依靠无源器件来调整特定应用的滤波器和控制回路。

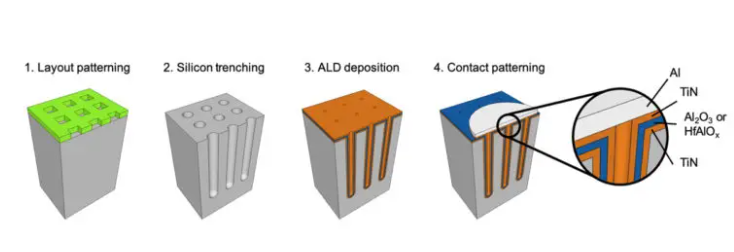

然而,半导体制造工艺的利用导致了许多用于高密度微电容器的新方法。Finish 公司 Picosun 使用其原子层沉积 ALD 设备,将导电 TiN 和绝缘电介质 Al 2 O 3和 HfAlO 3层的薄膜堆叠沉积到蚀刻到硅中的高纵横比沟槽中,从而将电容密度提高到 1 µF/mm 2。ALD 沉积和 3D 微电容器制造工艺如下图所示。

3D 微电容器制造的主要技术步骤。1:在硅表明产生方格孔洞;2:通过电化学微加工(ECM)对硅进行高纵横比开槽;3:保形金属-绝缘体-金属(MIM)叠层的原子层沉积(ALD);4:铝沉积和接触图案化。资料来源:皮科森

瑞典公司 Smoltek 在 EPCI PCNS会议上因其基于碳纳米纤维金属-绝缘体-金属 (CNF-MIM) 晶圆的半导体技术在 2019 年底实现了 +650nF/mm 2的电容密度而获得了杰出和最佳论文奖。他们使用ALD技术将Al2O3 /HfO2层沉积到碳纳米纤维3D结构上。

光纤长度仅为 2 – 3 µm,整个设备的总高度轮廓约为 4 µm。这使得电容器易于集成到 CMOS 芯片或 3D 堆叠中。

*博客内容为网友个人发布,仅代表博主个人自己的观点,如有侵权请联系工作人员删除。